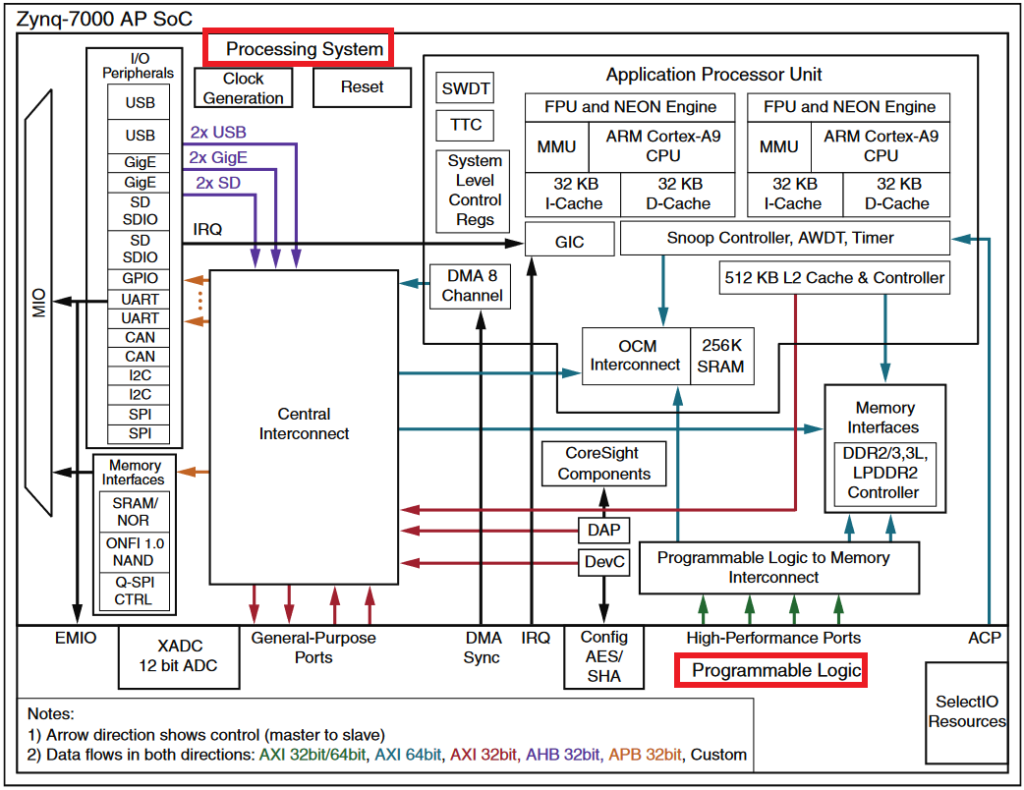

Zynqは、CPU(ARMコア)が搭載されているPS部(Processing System)と、従来のFPGA機能を持つPL部(Programmable Logic)の2つで構成されている。

PS部については、多くの組込みシステムと同様に、Ultra96-V2 ブートイメージ作成で作成したLinux上で動作する。

Zynqの大きな特徴がPL部である。

PL部は書き換え可能な巨大な回路群であり、ここに様々なユーザ回路を持たせて、PS部上のLinuxから制御することで、ユニークなシステム、しかもエンドユーザ先で変更可能、を形成することができる。

Contents

PL部 開発環境構築

PL部の開発はXilinx Vivadoで行うが、これは既にUltra96-V2 開発環境構築にて構築済み。

ここでは、Ultra96-V2用のBoard Fileの構築手順を記載する。

Board Fileは、通常の開発では基本的には使わず、自分で作成する必要があるが、開発キットなどは、開発元が用意しているので、これを使う。

Ultra96-V2用のBoard FileはAvnetが用意しているので、これをgit cloneして使う。

|

1 2 3 4 5 6 7 8 9 |

$ cd ~/git $ git clone https://github.com/Avnet/bdf.git Avnet_BDF Cloning into 'Avnet_BDF'... remote: Enumerating objects: 20, done. remote: Counting objects: 100% (20/20), done. remote: Compressing objects: 100% (17/17), done. remote: Total 277 (delta 4), reused 18 (delta 3), pack-reused 257 Receiving objects: 100% (277/277), 23.19 MiB | 1.81 MiB/s, done. Resolving deltas: 100% (101/101), done. |

git cloneしたディレクトリを、Vivadoのボードファイルフォルダにシンボリックリンクを貼る。

|

1 2 |

$ cd /opt/Xilinx/Vivado/2019.1/data/boards/board_files/ $ sudo ln -s <path_to>/git/Avnet_BDF Avnet_BDF |

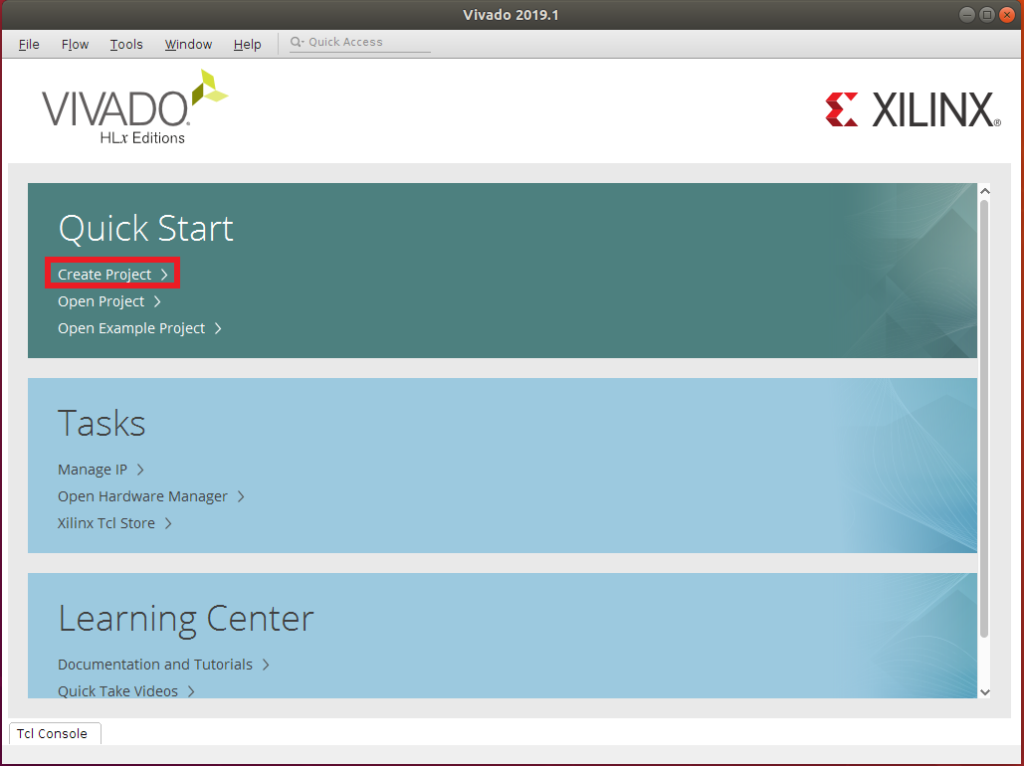

Vivadoプロジェクト作成

Create Projectでプロジェクトの新規作成

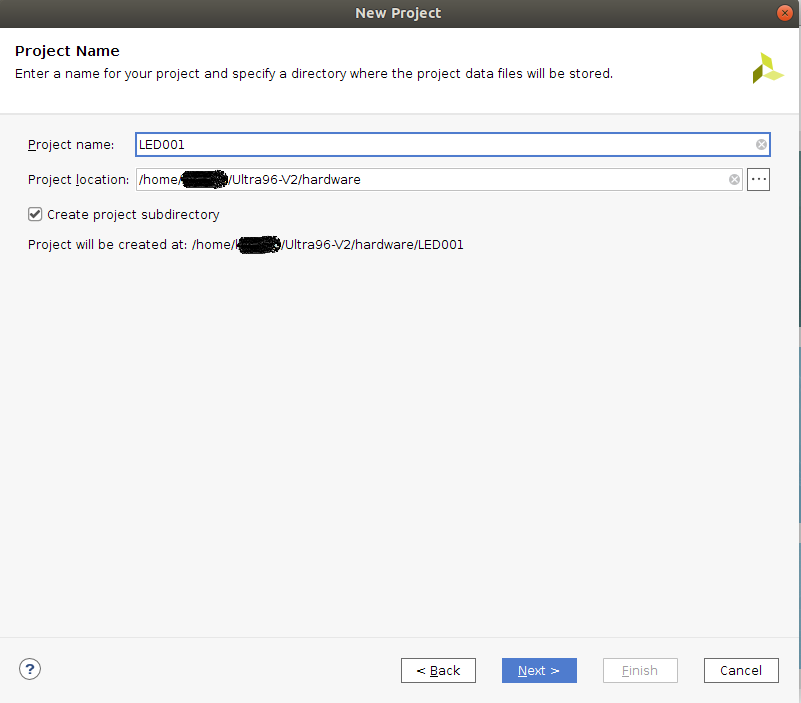

Project nameに適当な名前、Project locationに適当なディレクトリ(今回は/home/[USER]/Ultra96-V2/hardwareを指定)を入力して、次に進む。

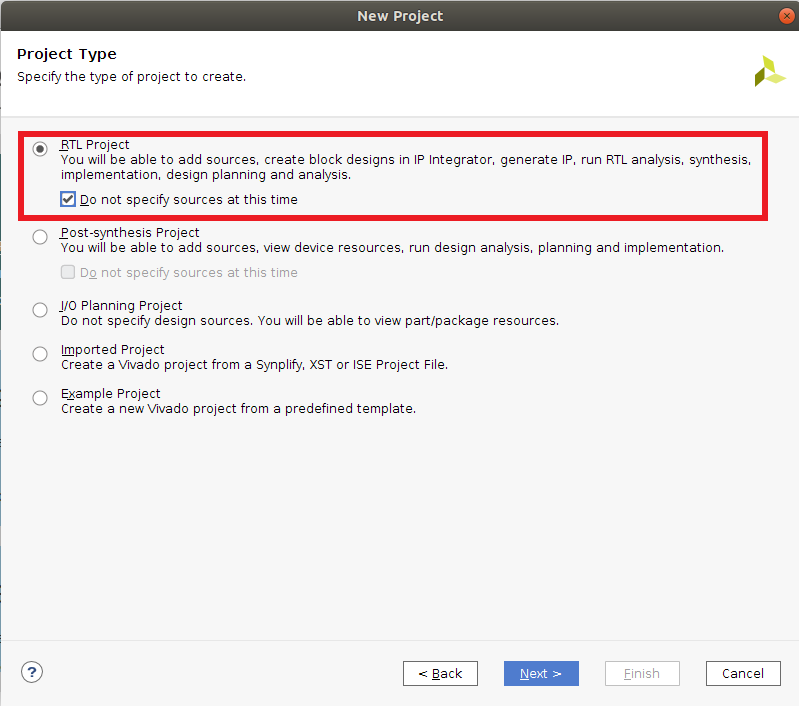

RTL Projectを選択。

今回は既存ソースは存在しないので、”Do not specify sources at this time”のチェックをつけておく。

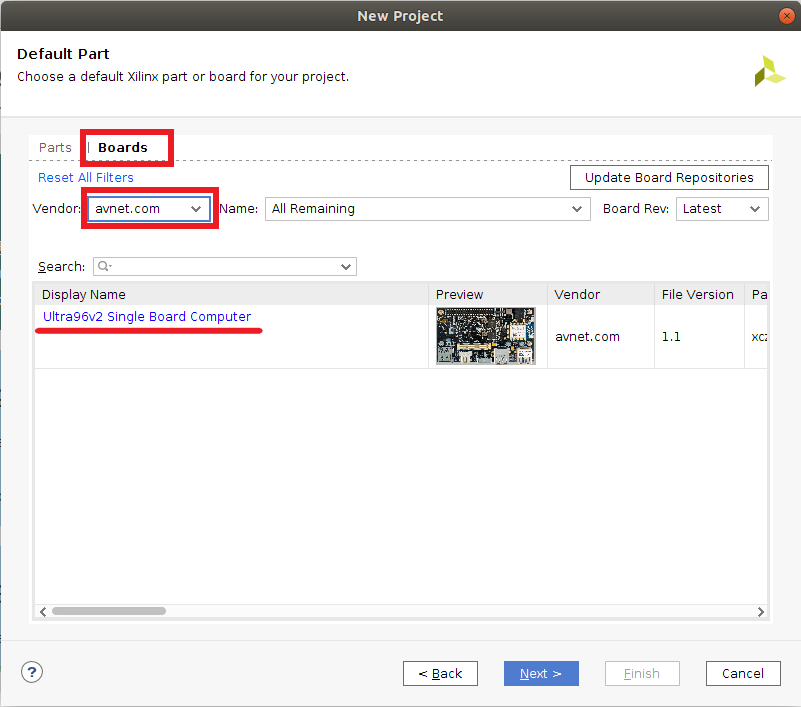

“Boards”タブに移動して、Vendorに”avnet.com”を選択すると、2020.7.26現在ではultra96v2のみが表示されるので、これを選択。

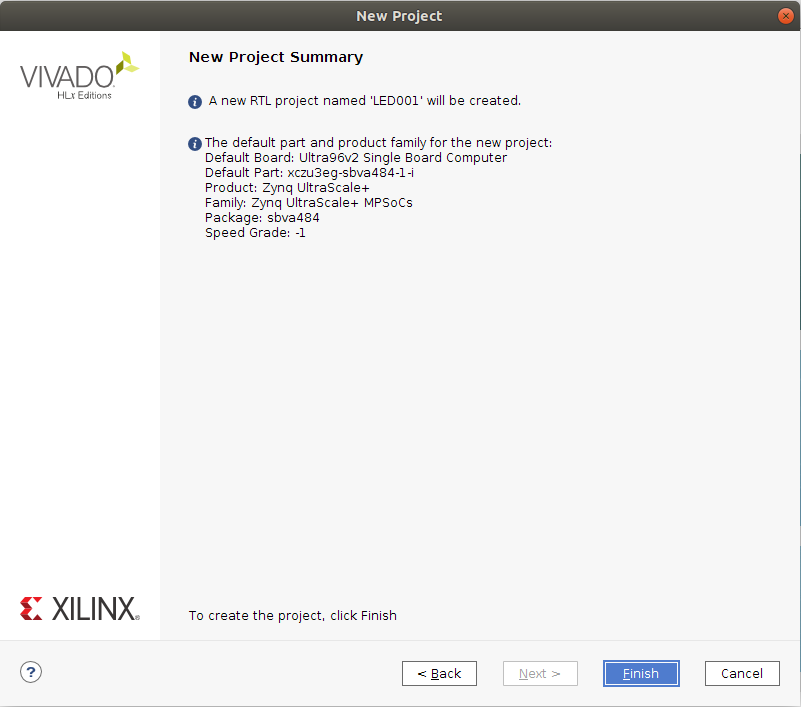

最後に以下のように各種設定情報が表示されるので、問題なければFinishする。

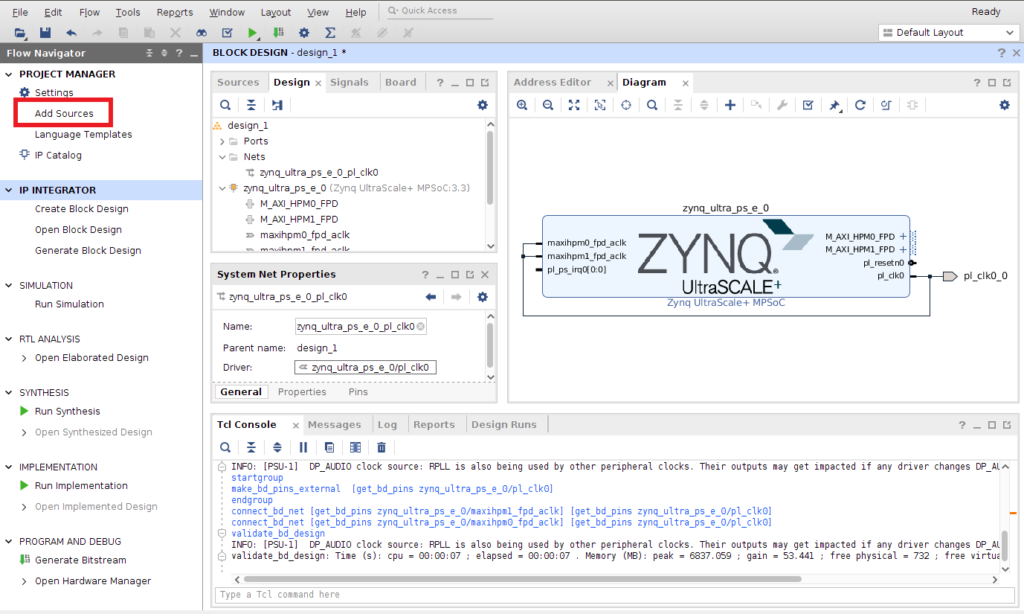

Block Design作成

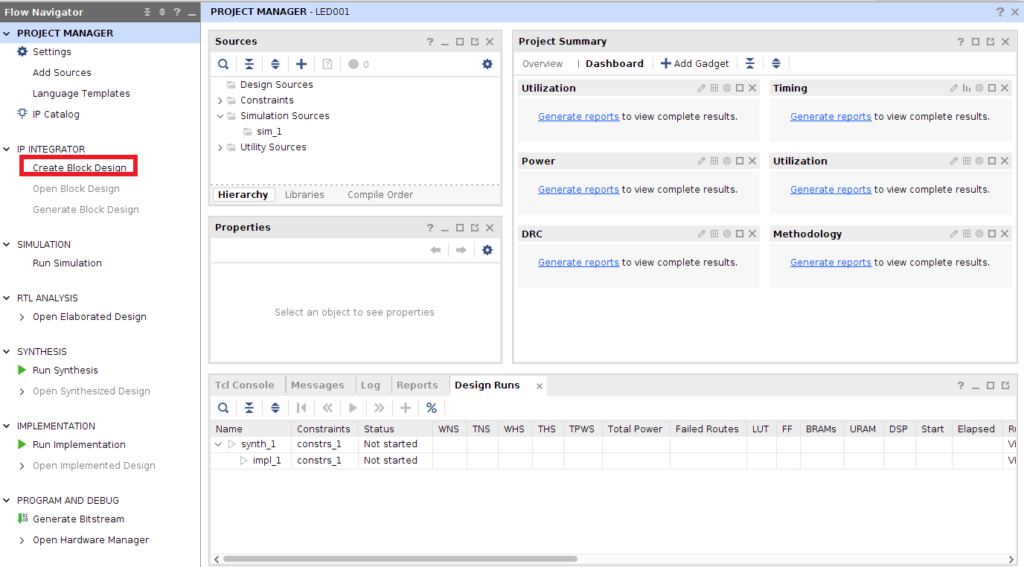

通常のFPGA作成と違い、まずはPS部との接続を宣言するために、Block Designを作成する。

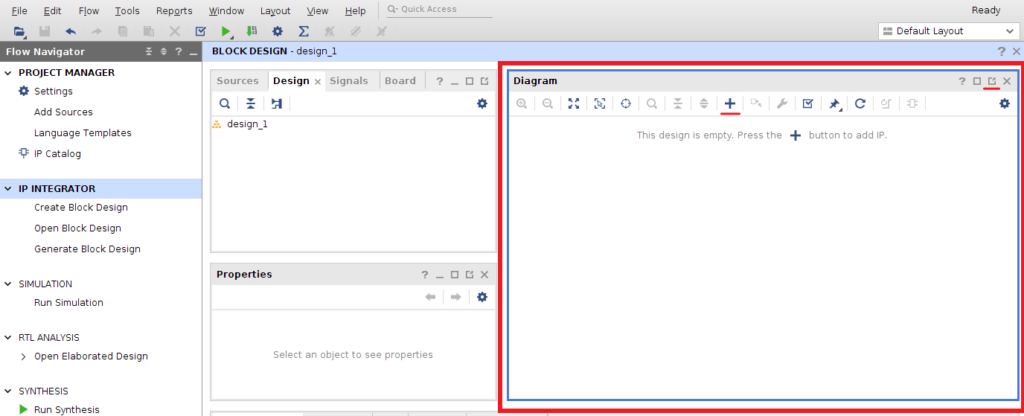

左メニューにある、”Create Block Design”をクリック。

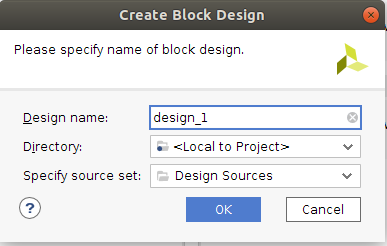

Design nameなどを尋ねられるが、デフォルトのままで作成。

右画面に”Diagram”というウィンドウが作成されるので、ここでBlock Designを作成していく。

画面小さいので、右上の×の隣のアイコンをクリックして、フローティングウィンドウに変更して作業を進めるのが良い。

ブロックの作成は+アイコンで行う。

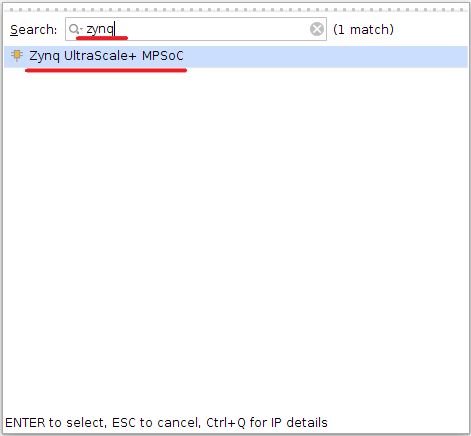

最初にZynqブロックを作成。

+アイコンをクリックして、Searchバーに”zynq”と打ち込むと現れる”Zynq Ultrascale+ MPSoC”をダブルクリック。

Diagramウィンドウにブロックが作成される。

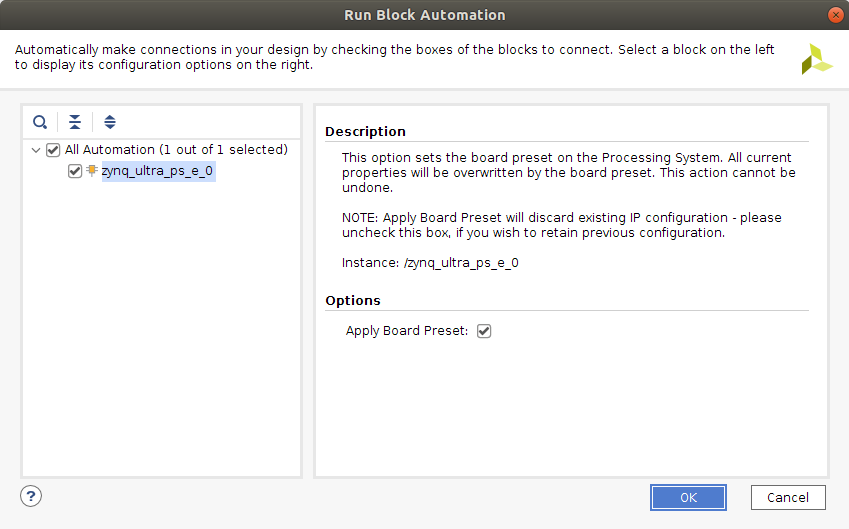

この状態で、まずは”Run Block Automation”をクリックする。

すると、以下が表示されるので、OKして実行する。

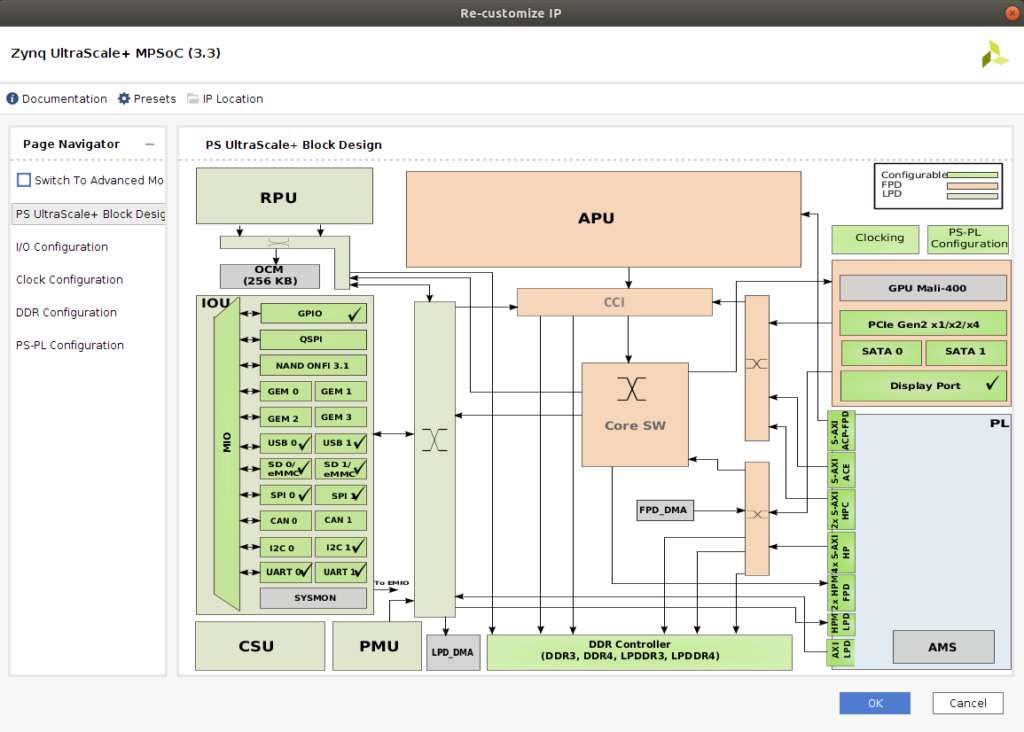

元の”Diagram”ウィンドウに戻って、Zynqブロックをダブルクリックして、PS部の設定を確認する。

この設定はブートイメージで作成したものと同じである必要がある。足りなかったり、違ったりするとまともにブートしないので注意が必要。

PL部との接続という意味では、以下を要確認。

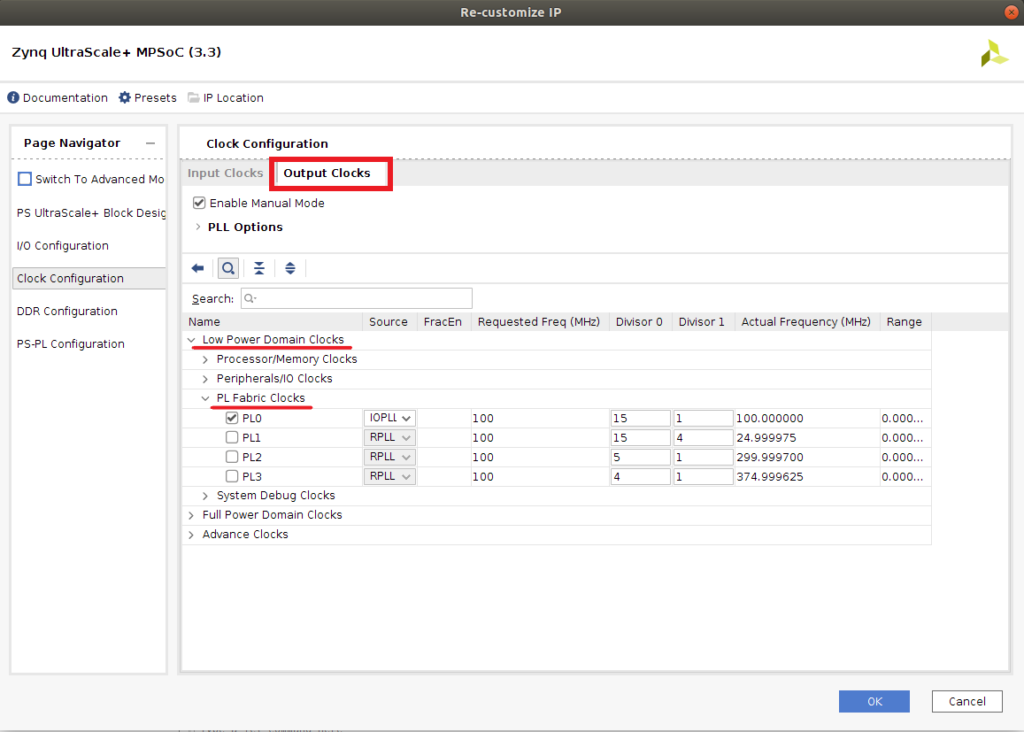

“Clock Configuration”の”Output Clocks”タブにある”PL Fabric Clocks”。

現在の設定は100MHz。

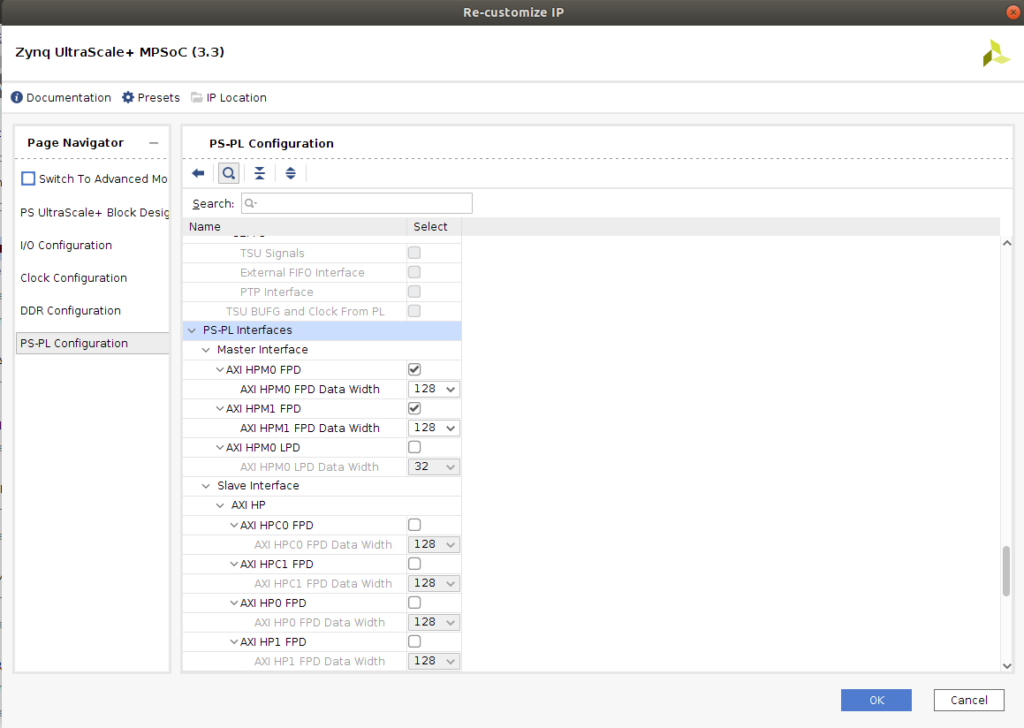

あとは、”PS-PL Configuration”。

デフォルトの設定では、Master InterfaceとしてAXI HPM0 FPD(128bits)と、AXI HPM1 FPD(128bits)がある。

元の”Diagram”ウィンドウに戻って、Block Designを作成。

まずは、先ほど確認したPL部用の100MHzクロックに名前を付けて、RTLソースから使用可能とする。

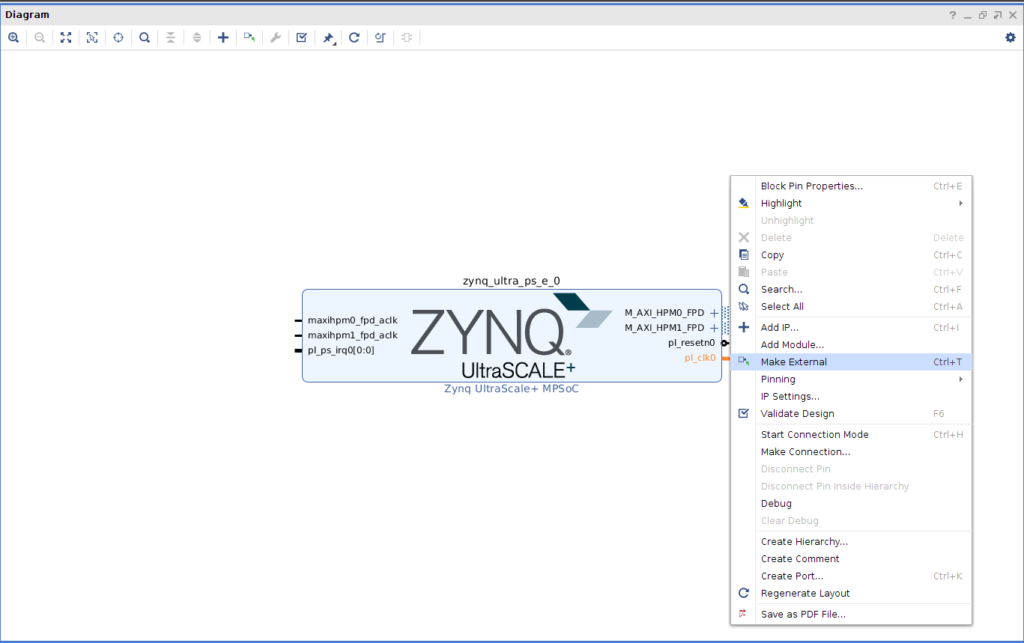

Zynqブロックのpl_clk0を右クリック->Make Externalして、外部ピンを作成。

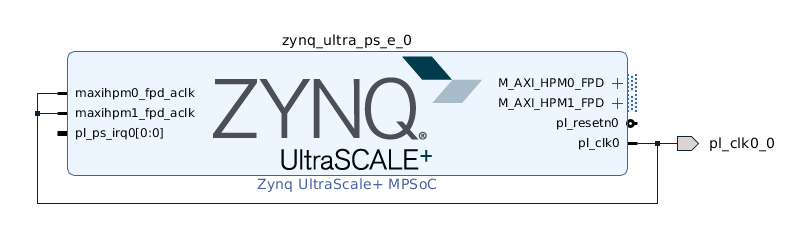

また、AXI HPM0 FPDとAXI HPM1 FPD用のクロックとして、この100MHzクロックを入力する。

ピンの先にマウスカーソルを合わせると、鉛筆アイコンになるので、その状態でpl_clk0までドラッグすると、結線される。

上記のように線を繋いだら、上メニューの”Validate Design”を実行。

これでBlock Designの準備は完了。

RTLソース記述

今回は単純にLEDにつながってるピンをON/OFFさせるだけのRTLを記述。

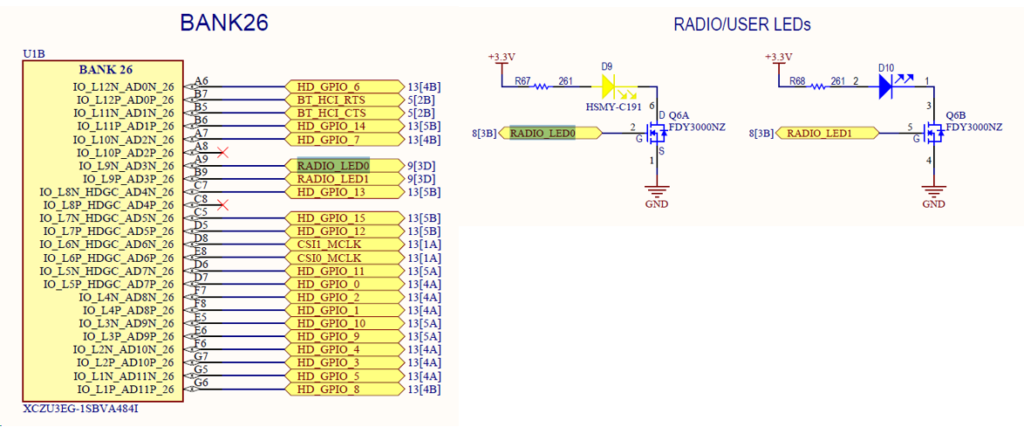

回路図から、”RADIO_LED0″信号につながっている、A9ピン(IO_L9N_AD3N_26)を制御する。

High出力でLEDオン、Low出力でLEDオフする。

Vivadoの左メニューにある”Add Sources”からRTLソースを追加。

“Add or create design sources” -> “Create File”で以下の新規ファイルを作成。

File type: Verilog

File name: Ultra96V2_Top

File location: <Local to Project>